FPGA Sipeed TangNANO

|

| Fig.1 Tarjeta TangNano 2704 (GW1N-1) |

Saludos cordiales, esperando aportar con un granito de arena en el aprendizaje de la electrónica digital, agradezco tu visita a mi blog, y recordar que cualquier sugerencia o critica constructiva sin duda me escriben a pablinza@me.com. Mencionar también que el propósito de la presente publicación solo tiene fines educativos.

Hoy quiero hacer una introducción y comentar acerca de una tarjeta de desarrollo, que tiene algo muy peculiar que sobresale con el resto de tarjetas; y es su reducido tamaño y precio me sin duda me da a entender que tengo a mano el dispositivo adecuado para introducir en la materia de sistemas digitales el uso de lenguajes descriptivos con la posibilidad de implementar los circuitos como parte de las experiencias que se pretende generar en las actividades efectuadas en laboratorio.

|

| Fig2. Elementos de la Tarjeta TangNANO |

Esta

tarjeta posee un chip FPGA GW1N-1 de la serie Litle Bee fabricado por Gowin Semiconductor, una empresa China relativamente nueva con respecto a otros fabricantes como Altera, Xilinx o Lattice. Viendo mas de cerca, la tarjeta comercializada por SIPEED con el sobrenombre de TangNANO, utiliza el chip GW1N-LV9QN48C6/I5 que físicamente se distingue por el encapsulado QFN-48, y representa el modelo mas básico de su serie, pero considerando los fines educativos para nuestro caso, podemos afirmar que cuenta con recursos suficientes para realizar nuestras practicas de laboratorio y particularmente la razón que mas relevancia tiene al menos desde mi perspectiva, es su bajo costo y la no dependencia de hardware adicional para depurar y cargar el firmare en la memoria, por lo que solo bastara conectarlo a un puerto USB de nuestro ordenador y empezar a trabajar con el.

Doy por entendido que ya se cuenta con conocimientos básicos de electrónica digital, dispositivos lógicos programables y lenguajes HDL. Si aun no estas familiarizado con las FPGA's aquí te dejo algunos enlaces muy interesantes:

https://www.fpga4fun.com/

https://www.nandland.com/

http://fpgalibre.sourceforge.net/

http://fpgawars.github.io/

https://www.youtube.com/watch?v=9KiCJ36Ol08

https://www.youtube.com/watch?v=i1utIs3y4QA

Introducción a la FPGA

Hablando del chip en si, el modelo GW1N-1 cuenta con un total de 1152 LUT's (Look-Up Tables), para tener una idea mas simple de esto podemos imaginar que cada LUT controla la función lógica de un elemento logico configurable, por lo tanto los valores de entrada a cada LUT se almacenaran en una memoria para configurar la estructura funcional del circuito que se va implementar.

Adicionalmente la FPGA GW1N-1 dispone de los siguientes elementos:

- 72Kbit de memoria en bloque B-SRAM con una disposición configurable.

- 96Kbit de memoria de usuario no volatil tipo FLASH.

- 864 Registros Bi-estables síncronos (FF)

- 41 pines de entrada y salida distribuidos en 4 bancos

La configuracion inicial que adquiere una FPGA es parte del proceso de carga del firmware en la que podemos considerar los siguientes dos escenarios:

Se establece temporalmente mediante JTAG, la configuracion de todos los elementos lógicos necesario de una FPGA para fines de prueba y depuración del circuito digital que se implementara. En este caso, la configuracion es volátil, y se perderá la funcionalidad cuando se reinicie el circuito.

Se transfiere la configuracion a una memoria no volátil, entonces cuando se energiza el circuito la FPGA configura toda su lógica desde esta memoria, para luego iniciar la funcionalidad del circuito implementado.

La placa TangNANO integra adicionalmente un chip de memoria PSRAM de 64Mbits que podrá utilizarse como recurso de almacenamiento temporal extra, también posee un cristal de 24MHz conectado a la entrada pin 35 (GCLKT2) , dos pulsadores con sus resistencias pull-up conectadas los pines 14/15, un led RGB conectado a los pines 16/17/18 y elementos necesarios para su puesta en marcha, facilitando la conectividad conforme a la siguiente distribución de pines.

|

| Fig3. Distribución de pines TangNANO |

Un aspecto importante de mencionar con respecto a esta tarjeta, es que no dispone una memoria externa para almacenar la configuracion o firmware del circuito por lo que los circuitos implementados con fines de prueba serán de forma temporal.

Software Gowin Requerido

Este FPGA es un producto creado por Gowinsemi, es decir que es propietario y necesitaremos utilizar software desarrollado por este fabricante, este software que consta principalmente de un IDE debemos descargar e instalar en nuestro ordenador para así trabajar con el desarrollo del circuito, para llevar esta instalación debemos seguir los siguientes pasos:

- Registrarse en la pagina de GoWin, <Click Aquí>;

- Ingresar con la cuenta registrada. <Click Aquí>;

- Descargar el software Gowin EDA Standard. <Click Aquí>;

- Solicitar la licencia completando el formulario. <Click Aquí>;

Después de 24 horas, Gowin le enviara la licencia al correo que registro en el formulario, y cuando proceda a instalar el software Gowin EDA Standard, al momento de iniciar por primera vez se le pedirá la activación con la licencia que le fue enviada.

Ya con el software Gowin EDA instalado sera posible diseñar y sintetizar nuestros circuitos digitales en la tarjeta TangNano.

|

| Fig4. Software Gowin EDA Standard |

Creación y configuración del proyecto Gowin

La versión utilizada al momento de crear esta entrada es la 1.9.8.10, luego de instalar y registrar la licencia, arrancaremos la aplicación de diseño GoWin FPGA Designer, y crearemos nuestro primer proyecto a través del menú File->New->FPGA Design Project.

|

| Fig5. Nombre del proyecto |

| ||||

| Fig6. Selección del dispositivo | |

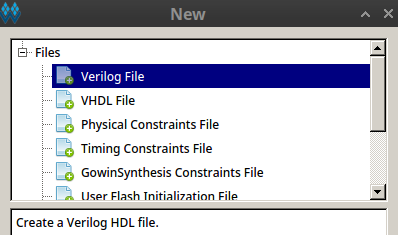

Una vez creado el proyecto, en la parte superior izquierda no aparece la estructura del proyecto, aquí agregaremos haciendo click derecho un par de archivos.

|

| Fig7. Adición de archivos al proyecto |

|

| Fig8. Adición de un archivo verilog |

|

| Fig9. Asignación de nombre al archivo |

El segundo archivo tiene como finalidad guardar el mapeo y configuración de las entradas y salidas del modulo descriptivo hacia los pines físicos de la FPGA, este archivo lo llamare tangnano.cst, haciendo referencia al modelo de tarjeta.

|

| Fig10. Archivo para el mapeo de pines |

|

| Fig11. Asignación del nombre al archivo |

Ahora la estructura final de nuestro proyecto, se vera como la imagen inferior, en este caso solo hay dos archivos que representan la estructura mínima para implementar un circuito digital.

|

| Fig12. Estructura final del proyecto |

Entonces es hora describir un circuito en el archivo testled.v, que va realizar una tarea bastante simple, un contador servirá para dividir la frecuencia principal del reloj de 24MHz a una frecuencia próxima al Herz, esto con el propósito de destellar de forma individual cada luz RGB integrado en la placa. Además el circuito también tendrá una entrada de reinicio con la que sera posible para y apagar el destello.

A continuación se muestra el código modulo testled con sus respectivos comentarios explicando con mayor detalle la operación del circuito.

input clk, rstn; //Entradas pines 35 y 14 reloj de 24MHz

output ledR, ledG, ledB; //Salidas pines 18, 17 y 16

reg [24:0] cnt; //Contador de 25-bit

reg [1:0] i; //Contador de 2-bit rango 0-3

reg [2:0] ledrgb;//Registro de 3-bit

assign {ledR, ledG, ledB} = ledrgb;//Señales RGB del LED asignado al registro

if(rstn == 0) ledrgb <= 3'b111;//Si rstn esta activo, LED Apagado

else

begin

if(i == 0) ledrgb <= 3'b111; //LED Apagado

if(i == 1) ledrgb <= 3'b110; //LED Color Azul

if(i == 2) ledrgb <= 3'b101; //LED Color Verde

if(i == 3) ledrgb <= 3'b011; //LED Color Rojo

i <= i + 1'b1; //Incrementa contador.

end

endmodule

Finalizada la edición necesitamos definir en la configuración del proyecto, menú Project-> Configuration el modulo top, que vendrá a ser el modulo testled que acabamos de crear, aquí solo se debe colocar el nombre.

| ||

| Fig13. Asignación del modulo Top | |

Ya con estos ajustes sera posible sintetizar el circuito para que luego procedamos a trabajar con el mapeo del circuito, el archivo del mapa físico tangnano.cst puede ser generado de manera gráfica haciendo click en la opción floor planner, aquí se creara una matriz con la asignación de todas la entradas y salidas del modulo, por lo que tocara determinar la asignación de pines físicos en la FPGA.

|

| Fig14. Asignación de pines en planificador |

Otra forma de crear este archivo de mapas es editar la configuración de forma manual, esto sin duda implica mas trabajo para el diseñador, en cualquiera de los casos el código sera el siguiente:

IO_LOC "ledB" 17;

IO_PORT "ledB" IO_TYPE=LVTTL33 PULL_MODE=NONE DRIVE=8 BANK_VCCIO=3.3;

IO_LOC "ledG" 16;

IO_PORT "ledG" IO_TYPE=LVTTL33 PULL_MODE=NONE DRIVE=8 BANK_VCCIO=3.3;

IO_LOC "ledR" 18;

IO_PORT "ledR" IO_TYPE=LVTTL33 PULL_MODE=NONE DRIVE=8 BANK_VCCIO=3.3;

IO_LOC "rstn" 14;

IO_PORT "rstn" IO_TYPE=LVTTL33 PULL_MODE=UP BANK_VCCIO=3.3;

IO_LOC "clk" 35;

IO_PORT "clk" IO_TYPE=LVTTL33 PULL_MODE=UP BANK_VCCIO=3.3;

Una vez realizada la asignación de pines nos sera posible generar las conexiones y ruteo que posibilita la creación de un bitstream o firmware del circuito digital, cuyo resultado se almacena en el fichero gwn1_test.fs. Este archivo deberá sera cargado a la FPGA.

Cargando el firmware a la FPGA

Este paso representa básicamente la implementación del circuito digital en la FPGA, en el caso de la tarjeta TangNano bastara con conectar a un puerto USB y proceder a la descarga del archivo gw1n_test.fs a la FPGA. Para llevar a cabo esta operación GoWin cuenta con el software de Programación GoWin Programmer pero debido a la compatibilidad entre versiones con mi ordenador Linux/Debian 12 he preferido utilizar openFPGALoader que es un software de distribución libre y con soporte para una gran variedad de tarjetas FPGA. El repositorio oficial es: https://github.com/trabucayre/openFPGALoader

Una vez instalado, bastara acceder a la linea de comandos, ingresar al directorio del proyecto, luego el subdirectorio /impl/prn donde se encuentra el firmware, y ejecutar la siguiente orden.

#openFPGALoader -m -b tangnano gw1n_test.fs

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse gw1n_test.fs: Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

Flash SRAM: [=============================] 100.00%

Done

Ahora nuestro circuito implementado ya debería estar funcionando en la FPGA

|

| Fig15. Funcionamiento del circuito |

Haz click <<aquí>> para descargar la carpeta del proyecto

Nuevamente quiero agradecer tu visita a mi blog, se que no detalle muchos pasos con relación a la instalación de los programas utilizados pero cualquier consulta al respecto puede escribirme al correo y con mucho gusto veré como colaborar.

Atentamente, Pablo Zárate A. email: pablinza@me.com / pablinzte@gmail.com, @pablinzar