FPGA Sipeed TangNANO

|

| Fig1. Tarjeta TangNANO9K |

Saludos

cordiales a los interesados en el mundo de la electrónica digital, agradezco tu visita a mi blog y quiero recordarte que

cualquier sugerencia o critica constructiva sera bienvenida, me pueden contactar con los datos que dejo al finalizar esta publicación. Mencionar también que el propósito de la presente

publicación solo tiene fines educativos.

Hoy quiero continuar con el aprendizaje de los dispositivos lógicos programables describiendo las características y el uso de una tarjeta de desarrollo TangNANO9K, que viene a ser una mejora de la primera que publique en un entrada anterior. Esta tarjeta mantiene su reducido tamaño y bajo precio que lo hace ideal para utilizar las practicas de laboratorio de la materia Sistemas Digitales. Además se pretende hacer uso de lenguajes descriptivos HDL con la posibilidad de implementar los circuitos digitales de baja a mediana complejidad generando así experiencias de trabajo.

Esta

tarjeta posee un chip FPGA GW1NR-9C de la serie Litle Bee fabricado por Gowin Semiconductor,

una empresa China relativamente nueva con respecto a otros fabricantes

como Altera, Xilinx o Lattice. La tarjeta

en particular esta construida y comercializada por SIPEED con el sobrenombre de TangNANO 9K, integrando el

chip GW1NR-LV9QN88PC6/I5 y representa un modelo intermedio de su serie, por lo que tomando en cuenta

los fines educativos podemos deducir que la misma dispone de

recursos suficientes para realizar nuestras practicas de laboratorio, además su bajo costo y la integración del hardware adicional

nos permitirá cargar y depurar el firmware conectando al puerto USB de nuestro ordenador.

Doy por entendido que ya se cuenta con conocimientos básicos de electrónica digital, dispositivos lógicos programables y lenguajes HDL. Si aun no estas familiarizado con las FPGA's aquí te dejo algunos enlaces muy interesantes:

https://www.fpga4fun.com/

https://www.nandland.com/

http://fpgalibre.sourceforge.net/

http://fpgawars.github.io/

https://www.youtube.com/watch?v=9KiCJ36Ol08

https://www.youtube.com/watch?v=i1utIs3y4QA

Introducción a la FPGA

Hablando del chip en si, el modelo GW1NR-9C cuenta con un total de 8648 LUT's (Look-Up Tables), para tener una idea mas simple podemos imaginar que estas FPGA disponen principalmente de dos elementos denominados como Unidad Lógica Configurable (CLU) y Unidad Funcional Configurable (CFU), entonces la configuracion lógica de estos elementos es controlada por las LUT. Por lo general las LUT son de cuatro entradas LUT-4, pero pueden interconectarse para formar LUT de mas entradas, son como las tabla de verdad pero con las salidas pre-establecidas durante el proceso de sintensis.

Adicionalmente la FPGA GW1NR-9C dispone de los siguientes elementos:

- 468Kbit de memoria en bloque B-SRAM con una disposición configurable.

- 17280 bits de memoria Shadow S-SRAM

- 608Kbit de memoria de usuario no volátil tipo FLASH.

- 6480 Registros Bi-estables síncronos (FF)

- 41 pines de entrada y salida distribuidos en 4 bancos

- 64Mbit de memoria SDRAM

- 20 Multiplicadores 18x18 y 2 PLL

La configuracion inicial que adquiere una FPGA es parte del proceso de carga del firmware en la que podemos considerar los siguientes escenarios:

Se establece temporalmente mediante JTAG, la configuracion de todos los elementos lógicos necesario

de una FPGA para fines de prueba y depuración del circuito digital que

se implementara. En este caso, la configuracion es volátil, y se perderá

la funcionalidad cuando se reinicie el circuito.

Se transfiere la configuracion a una memoria no volátil, entonces cuando se energiza el circuito la FPGA configura toda su lógica desde esta memoria, para luego iniciar la funcionalidad del circuito implementado.

|

| Fig2. Elementos de la Placa TangNANO9K |

La placa TangNANO 9K integra adicionalmente los siguientes elementos:

- Un chip de memoria FLASH de 32Mbits para guardar el firmware

- Un cristal de 27MHz conectado a la entrada pin 52(GCLKT1)

- Dos pulsadores con resistencias pull-up conectadas los pines 3 y 4

- Seis leds conectados a los pines 10,11,13,14,15 y 16

- Puerto de salida a pantalla RGB/LCD y HDMI

- Puerto lector de memorias microSD

- Puerto de carga y depuración USB-C

La integración de todos estos elementos facilita la conectividad y puesta en marcha de los circuitos que vamos a elaborar, conforme a la siguiente distribución de pines.

|

| Fig3. Mapa de pines Tangnano9k (src: wiki.sipeed.com) |

A diferencia de la tangnano original esta tarjeta si cuenta con una memoria no volátil externa de 32Mbit que permitirán la carga de firmware a la FPGA de manera permanente.

Software Gowin Requerido

Este FPGA es un producto creado por Gowinsemi, es decir que es propietario y necesitaremos utilizar software desarrollado por este fabricante, este software que consta principalmente de un IDE debemos descargar e instalar en nuestro ordenador para así trabajar con el desarrollo del circuito, para llevar esta instalación debemos seguir los siguientes pasos:

- Registrarse en la pagina de GoWin, <Click Aquí>;

- Ingresar con la cuenta registrada. <Click Aquí>;

- Descargar el software Gowin EDA Standard. <Click Aquí>;

- Solicitar la licencia completando el formulario. <Click Aquí>;

Después

de 24 horas, Gowin le enviara la licencia al correo que registro en el

formulario, y cuando proceda a instalar el software Gowin EDA Standard,

al momento de iniciar por primera vez se le pedirá la activación con la

licencia que le fue enviada.

Ya con el software Gowin EDA instalado sera posible diseñar y sintetizar nuestros circuitos digitales en la tarjeta TangNano9K.

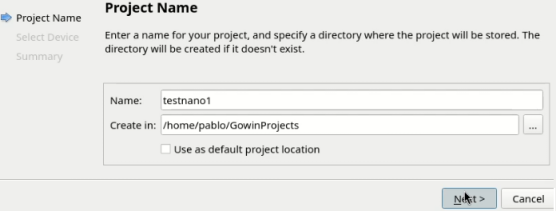

Creación y configuración del proyecto Gowin

La versión utilizada al momento de crear esta entrada es la 1.9.11.02, luego de instalar y registrar la licencia, arrancaremos la aplicación de diseño GoWin FPGA Designer, y crearemos nuestro primer proyecto a través del menú File->New->FPGA Design Project.

|

| Fig4. Asignación del nombre de proyecto Gowin |

Luego de establecer la ruta o carpeta de trabajo y el nombre de nuestro proyecto testnano1, el asistente nos pedirá la informacion del chip FPGA que utilizaremos.

|

| Fig5. Selección del dispositivo FPGA |

|

| Fig6. Resumen de la configuracion inicial |

Luego de completar la configuracion inicial, agregaremos al proyecto nuestro primer archivo verilog, para esto seleccionamos a través del menú File->New->Verilog File, y completo el nombre del archivo que en mi caso coloque top.

|

| Fig7. Creación del archivo Verilog |

A continuación se muestra el código modulo del modulo top.v con sus respectivos comentarios explicando con mayor detalle la operación del circuito, escribimos este código a nuestro archivo tal como se observa en la figura 8.

module top(but1, but2, led1, led2);

input but1, but2; //define las dos entradas

output led1, led2; //define las dos salidas

assign led1 = but1;//asigna al led1 el estado del but1

assign led2 = but2;//asigna al led1 el estado del but1

endmodule

|

| Fig8. Modulo descriptivo top.v |

Luego debemos agregar una archivo que se utiliza para describir la asignación de pines y su restricción, para esto seleccionamos a través del menú File->New->Physical Constraint File y completo el campo con el nombre top.cst

| |

| Fig9. Creación del archivo de asignación |

Una vez creado el archivo podemos encontrar en la barra de iconos la opción para abrir el FloorPlanner, en la que escribiremos la asignación de pines físicos a los entradas y salidas declaradas en el modulo descriptivo top.v, es importante que antes realizar esta asignación el código verilog sea sintetizado sin errores.

|

| Fig10. Barra de iconos (FloorPlanner) |

|

| Fig11. Asignación de pines en (I/O constraint) |

Finalmente FloorPlanner nos genera automáticamente el código del archivo top.cst por lo que ahora nos queda solamente hacer la sintentizacion y ruteo del proyecto, tal como se puede ver en la siguiente imagen.

|

| Fig12. Archivo de Asignación física para ruteo final |

Ahora tenemos listo los archivos generados en la carpeta /impl/pnr dentro de la carpeta de nuestro proyecto, entre estos archivos se encuentra el firmware o bitstream que deberá cargarse a la FPGA, este archivo contiene la configuracion de todas la LUTS y recursos adicionales.

Cargando el firmware a la FPGA

|

| Fig13. Ejecución de Gowin Programmer |

Una

vez instalado, bastara acceder a la linea de comandos, ingresar al

directorio del proyecto, luego a la subcarpeta /impl/prn donde se

encuentra el firmware, y ejecutar la siguiente orden.

#openFPGALoader -m -b tangnano testnano1.fs

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

Flash SRAM: [=============================] 100.00%

Done

Si nuestro fin es cargar el firmware de forma permanente, entonces debemos transferir el archivo a la memoria FLASH que integra la tarjeta, aplicando el siguiente comando: #openFPGALoader -f -b tangnano testnano1.fs

En este momento el circuito que hemos diseñado ya debería estar funcionando.

Como

resumen de todo lo descrito en la sección, te dejo un vídeo donde se

observa la creación e implementación del proyecto con el software GoWin

EDA y también el acceso al repositorio GOLAB1 donde alojare algunos ejemplos de uso para esta tarjeta.

Atentamente, Pablo Zárate A. email: pablinza@me.com / pablinzte@gmail.com, @pablinzar